# SMiTe: Precise QoS Prediction on Real-System SMT Processors to Improve Utilization in Warehouse Scale Computers

Yunqi Zhang, Michael A. Laurenzano, Jason Mars, Lingjia Tang Clarity-Lab, Electrical Engineering and Computer Science, University of Michigan, Ann Arbor

#### **Goal: Improve Data Center Utilization**

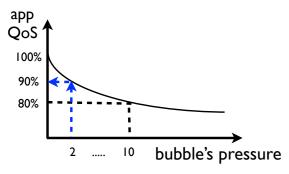

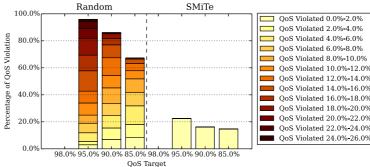

Precise interference prediction identifies "safe" co-locations to improve server utilization

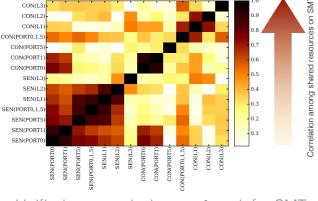

### SMT Co-location is Harder than CMP

Unified approach for CMP co-location

Unified approach does **not** work for SMT

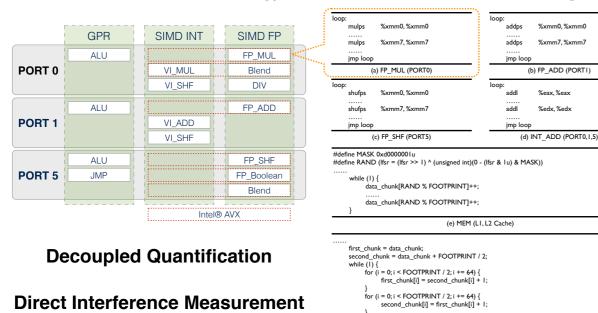

(f) MEM (L3 Cache)

%xmm0, %xmm0

%xmm7, %xmm7

(b) FP\_ADD (PORTI)

%eax %eax

%edx %edx

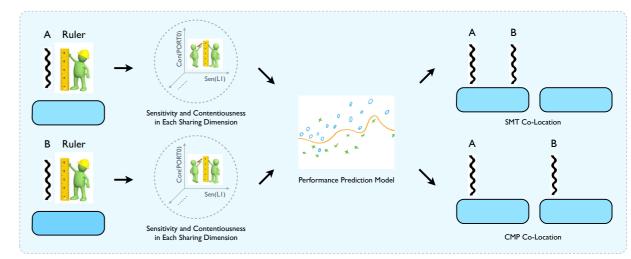

**Solution: Ruler-based Methodology** Max utilization in each resource sharing dimension

SMiTe Methodology Overview

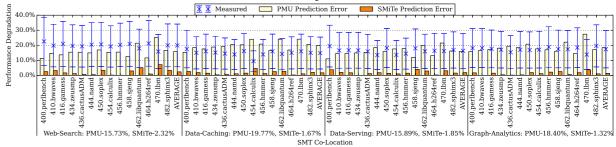

#### Precise Interference Prediction on Real-System SMT Processors

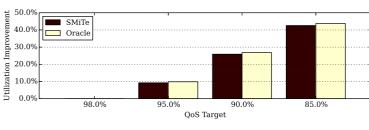

#### Data Center Utilization Improvement

# **Commodity Processor**

< 2% Prediction Error

## 42% Utilization Improvement